集成電路(IC)設計是現代電子技術的核心,而模擬集成電路設計在其中占據重要地位,尤其是運算放大器(Op-Amp)作為關鍵構建模塊,廣泛應用于信號處理、電源管理和通信系統中。本文將從運算放大器的基礎原理出發,探討模擬集成電路設計的關鍵技術、應用領域以及當前面臨的挑戰。

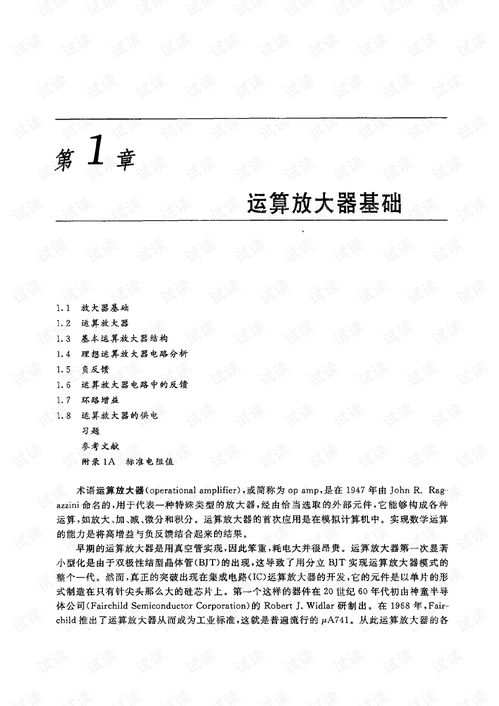

一、運算放大器:模擬設計的基石

運算放大器是一種高增益的差分放大器,具有高輸入阻抗和低輸出阻抗的特性。其理想模型包括無限大的開環增益、無限寬的帶寬和零輸入偏置電流,但在實際設計中,這些參數受到工藝和功耗的限制。典型的運算放大器由輸入級、增益級和輸出級組成:輸入級通常采用差分對結構,以抑制共模噪聲;增益級提供電壓放大;輸出級則確保驅動能力。例如,在CMOS工藝中,運算放大器設計需權衡增益、帶寬、功耗和噪聲性能,常見拓撲包括兩級運放和折疊共源共柵結構。

二、模擬集成電路設計的關鍵技術

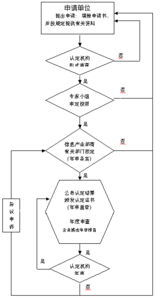

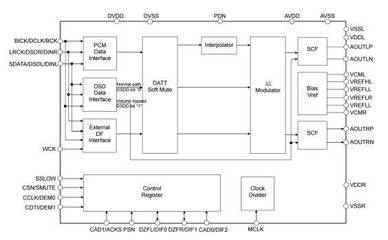

模擬集成電路設計涉及從系統規格到物理實現的完整流程。設計師需根據應用需求定義性能指標,如增益、帶寬、功耗和線性度。隨后,進行電路拓撲選擇和器件尺寸優化,這通常依賴于SPICE仿真工具來驗證直流、交流及瞬態特性。在版圖設計階段,匹配性、寄生效應和熱穩定性成為關鍵考量,例如通過共質心布局來減少工藝偏差。現代模擬設計越來越多地與數字電路集成,形成混合信號系統,這要求設計師掌握信號完整性和電源管理知識。

三、應用領域與實例分析

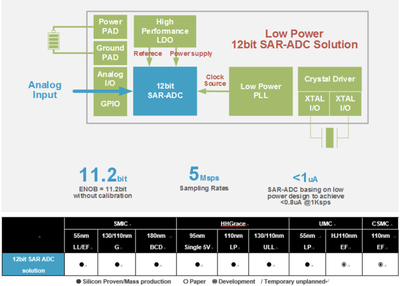

運算放大器和模擬集成電路在眾多領域發揮著不可替代的作用。在醫療電子中,高精度運放用于生物信號采集,如心電圖(ECG)設備,要求低噪聲和高共模抑制比。在音頻處理中,Class-D放大器利用PWM調制實現高效功率放大。汽車電子中的傳感器接口電路也依賴模擬IC,用于處理溫度、壓力信號。一個典型實例是數據轉換器(ADC/DAC),其中運算放大器作為采樣保持電路的核心,確保轉換精度。隨著物聯網(IoT)和5G技術的發展,低功耗、高集成度的模擬設計需求日益增長。

四、當前挑戰與未來趨勢

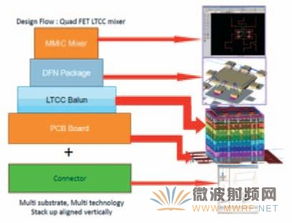

盡管技術進步顯著,模擬集成電路設計仍面臨多重挑戰。工藝尺寸的縮小導致器件非理想性加劇,如短溝道效應和漏電流,影響模擬性能。電源電壓的降低限制了動態范圍,設計師需創新電路結構,如使用斬波穩定技術來降低失調電壓。模擬設計的自動化程度遠低于數字設計,依賴工程師經驗,這增加了開發周期和成本。未來,趨勢將聚焦于人工智能輔助設計、更先進的工藝節點(如FinFET)以及系統級封裝(SiP)技術,以提升性能并降低功耗。

運算放大器和模擬集成電路設計是電子工程的支柱,其發展推動著從消費電子到工業控制的創新。設計師需不斷平衡理論知識與實踐技巧,以應對日益復雜的應用需求。