數字集成電路設計是電子工程領域的核心課程之一,第六章通常涉及時序邏輯電路、觸發器、狀態機設計等關鍵概念。以下是針對該章節的典型習題及詳細答案解析,旨在幫助學習者鞏固理論知識并提升實踐能力。

習題1:時序邏輯電路分析

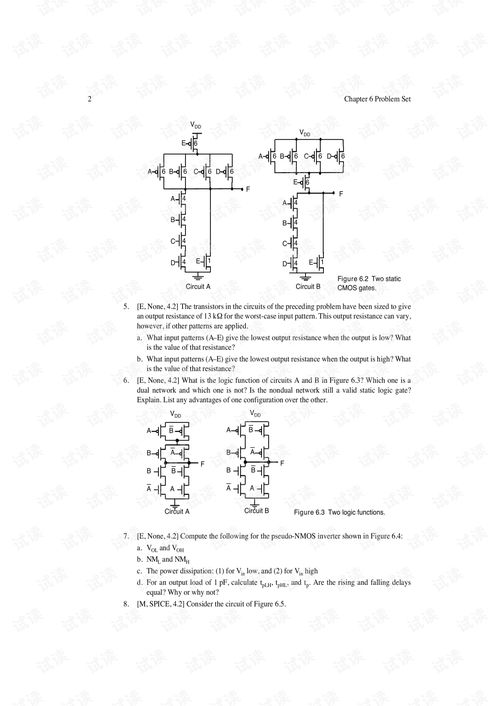

題目:分析圖6-1所示時序邏輯電路,寫出其狀態表和狀態圖,并說明電路功能。

答案解析:

識別電路中的觸發器類型(如D觸發器或JK觸發器),并列出輸入、輸出和狀態變量。通過狀態方程推導狀態轉移表,繪制狀態圖。例如,若電路為3位計數器,狀態圖將顯示循環計數模式。結論應指出電路的具體功能,如模8計數器或序列檢測器。

習題2:觸發器設計

題目:設計一個邊沿觸發的D觸發器,要求使用基本門電路實現,并分析其建立時間和保持時間。

答案解析:

D觸發器的設計通常基于主從結構或使用傳輸門。步驟包括:繪制電路圖,解釋時鐘信號邊沿(上升沿或下降沿)對數據鎖存的影響。建立時間指數據在時鐘邊沿前必須穩定的最小時間,保持時間指時鐘邊沿后數據需保持的時間。通過時序圖分析這些參數,確保電路在高速下可靠工作。

習題3:有限狀態機(FSM)設計

題目:設計一個Moore型有限狀態機,檢測輸入序列“1010”,當檢測到完整序列時輸出高電平。

答案解析:

首先定義狀態:S0(初始)、S1(收到1)、S2(收到10)、S3(收到101)、S4(收到1010)。繪制狀態轉移圖,基于輸入位(0或1)確定下一狀態。輸出僅與當前狀態相關,S4狀態輸出1。使用狀態表或VHDL/Verilog代碼實現,并驗證其功能通過仿真測試。

習題4:時序優化

題目:給定一個組合邏輯電路與時序路徑,計算最大時鐘頻率,并討論如何通過流水線技術提高性能。

答案解析:

最大時鐘頻率由關鍵路徑延遲決定,公式為 \( f{max} = 1 / T{clk} \),其中 \( T_{clk} \) 包括觸發器延遲和組合邏輯延遲。通過添加流水線寄存器,將長路徑分割為多個階段,減少每級延遲,從而提升頻率。舉例說明流水線如何增加吞吐量,但可能引入額外延遲和面積開銷。

綜合練習

題目:結合第六章內容,設計一個簡單的數字系統,如交通燈控制器,要求使用狀態機并考慮時序約束。

答案解析:

定義狀態(如紅燈、綠燈、黃燈),輸入(定時器信號),輸出(燈控制信號)。使用狀態機描述狀態轉移,確保每個狀態持續時間符合安全標準。時序分析包括檢查建立/保持時間,避免亞穩態。通過仿真驗證功能,并討論實際應用中的功耗和面積優化策略。

總結

第六章習題覆蓋了數字集成電路設計的核心時序概念,通過動手分析和設計,學習者能加深對觸發器、狀態機和時序優化理解。建議結合EDA工具進行仿真,以強化實踐技能。