CPLD(復雜可編程邏輯器件)是一種基于可編程邏輯技術的半導體設備,廣泛應用于數字電路設計領域。它通過可編程互連資源將多個邏輯塊連接起來,能夠實現復雜的組合邏輯和時序邏輯功能。

CPLD的核心結構通常包括可編程邏輯單元(如宏單元)、可編程互連陣列和輸入/輸出模塊。與FPGA相比,CPLD具有更確定的時序特性、更快的上電啟動時間和更簡單的編程架構。其非易失性特性使得配置信息在斷電后仍能保留,無需每次上電重新加載。

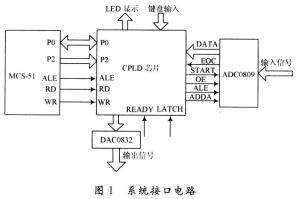

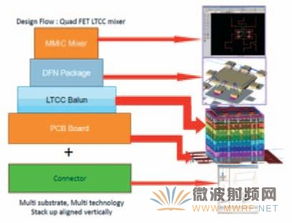

在應用方面,CPLD主要用于地址解碼、接口轉換、狀態機控制、時鐘管理等場景。在工業控制、通信設備、消費電子和汽車電子等領域都有廣泛應用。工程師通常使用硬件描述語言(如VHDL或Verilog)進行設計,然后通過專用開發工具進行綜合、布局布線和編程。

隨著技術進步,CPLD在集成度、性能和功耗方面持續優化,雖然面臨FPGA的競爭,但在許多對成本、功耗和確定性要求較高的應用中仍保持重要地位。