集成電路(Integrated Circuit, IC)設(shè)計是一個復(fù)雜而精密的過程,它通常被劃分為前端設(shè)計和后端設(shè)計兩大階段。前端設(shè)計側(cè)重于邏輯功能與架構(gòu),而后端設(shè)計的核心,便是物理設(shè)計(Physical Design),以及支撐其高效實現(xiàn)的軟件開發(fā)。物理設(shè)計與軟件開發(fā)相輔相成,共同決定了芯片的最終性能、功耗、面積和可制造性。

一、物理設(shè)計:從網(wǎng)表到版圖的藝術(shù)與科學(xué)

物理設(shè)計是IC設(shè)計流程中承上啟下的關(guān)鍵環(huán)節(jié)。它的任務(wù)是將前端設(shè)計產(chǎn)生的、用硬件描述語言(如Verilog/VHDL)描述的邏輯網(wǎng)表(Netlist),轉(zhuǎn)化為可供芯片制造工廠(Foundry)使用的物理版圖(Layout)。這個過程主要包括以下幾個核心步驟:

- 布圖規(guī)劃(Floorplanning):如同建筑設(shè)計的總體布局,需要確定芯片的核心區(qū)域、輸入輸出(I/O)引腳位置、電源網(wǎng)絡(luò)規(guī)劃以及各個功能模塊(宏模塊、存儲器等)的粗略擺放。優(yōu)秀的布圖規(guī)劃是后續(xù)步驟成功的基礎(chǔ),直接影響芯片的時序、功耗和面積。

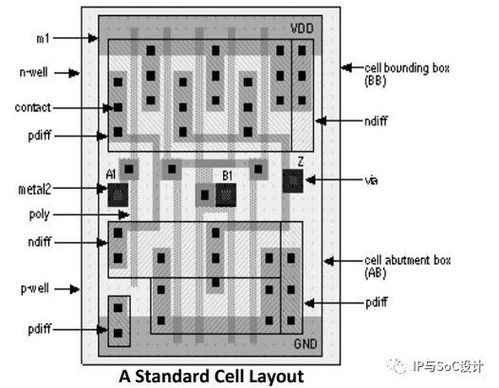

- 布局(Placement):將網(wǎng)表中的所有標(biāo)準(zhǔn)單元(Standard Cell)和宏模塊精確地放置在芯片的特定位置上。布局的目標(biāo)是在滿足時序要求的最小化互聯(lián)線長,以降低延遲和功耗。

- 時鐘樹綜合(Clock Tree Synthesis, CTS):構(gòu)建一個低偏斜(Skew)、低延遲的全局時鐘分布網(wǎng)絡(luò)。時鐘信號是芯片的“心跳”,其質(zhì)量直接關(guān)系到整個芯片能否在目標(biāo)頻率下穩(wěn)定工作。CTS是物理設(shè)計中至關(guān)重要且極具挑戰(zhàn)性的一環(huán)。

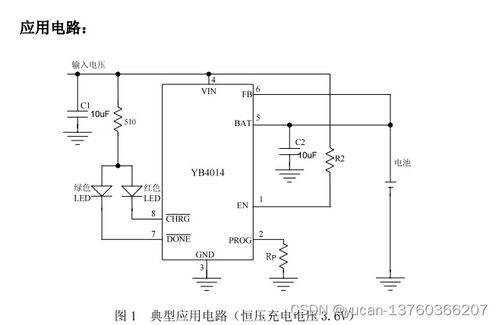

- 布線(Routing):在布局確定的單元之間,根據(jù)電學(xué)規(guī)則和設(shè)計規(guī)則,實際連接金屬導(dǎo)線。布線分為全局布線和詳細(xì)布線,必須解決數(shù)以億計的互聯(lián)問題,同時避免信號完整性(如串?dāng)_)、電遷移和天線效應(yīng)等問題。

- 物理驗證與簽核(Physical Verification & Sign-off):在版圖完成后,進(jìn)行一系列嚴(yán)格的檢查,包括設(shè)計規(guī)則檢查(DRC)、版圖與電路圖一致性檢查(LVS)、電氣規(guī)則檢查(ERC)以及寄生參數(shù)提取(PEX)后的時序、功耗簽核分析。只有通過所有驗證,版圖才能交付流片。

二、軟件開發(fā):物理設(shè)計的引擎與基石

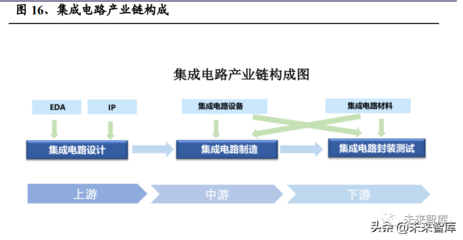

如此復(fù)雜的物理設(shè)計過程,絕非手工可以完成。它高度依賴于一套強(qiáng)大、成熟的電子設(shè)計自動化(EDA)軟件工具鏈。這些軟件的開發(fā),是計算機(jī)科學(xué)、應(yīng)用數(shù)學(xué)和半導(dǎo)體物理的深度交叉領(lǐng)域。

- 核心算法與引擎:物理設(shè)計軟件的核心是解決一系列NP難或NP完全的組合優(yōu)化問題。例如,布局問題可以建模為帶約束的二次分配問題,布線問題則涉及圖論和迷宮算法。軟件開發(fā)團(tuán)隊需要研發(fā)高效的啟發(fā)式算法(如模擬退火、遺傳算法)、解析算法以及基于機(jī)器學(xué)習(xí)/AI的新方法,以在可接受的時間內(nèi)求解超大規(guī)模(數(shù)億個晶體管)的問題。

- 設(shè)計與工藝的橋梁:EDA軟件必須緊密跟隨半導(dǎo)體制造工藝的演進(jìn)。軟件開發(fā)需要集成并精確建模 Foundry 提供的工藝設(shè)計套件(PDK),包括工藝文件、設(shè)計規(guī)則文件、標(biāo)準(zhǔn)單元庫、寄生參數(shù)模型等。軟件對先進(jìn)工藝(如FinFET、GAA)的支持能力,直接決定了設(shè)計公司能否利用最新工藝實現(xiàn)芯片。

- 工具鏈集成與流程自動化:一個完整的物理設(shè)計流程涉及數(shù)十款工具(來自Synopsys, Cadence, Siemens EDA等廠商或自研工具)。軟件開發(fā)不僅包括單個工具,更重要的是構(gòu)建一個高度集成、數(shù)據(jù)互通、可腳本化(常用Tcl、Python)的自動化流程平臺。這能極大提升設(shè)計效率,減少人為錯誤,并支持“設(shè)計空間探索”(Design Space Exploration)。

- 并行計算與大數(shù)據(jù)處理:現(xiàn)代芯片設(shè)計數(shù)據(jù)量龐大,一次全芯片的寄生參數(shù)提取可能產(chǎn)生TB級的數(shù)據(jù)。因此,EDA軟件的開發(fā)必須充分利用多核CPU、分布式計算、GPU加速等技術(shù),以縮短運(yùn)行時間。需要開發(fā)高效的數(shù)據(jù)管理和分析工具來處理和可視化這些設(shè)計數(shù)據(jù)。

三、物理設(shè)計與軟件開發(fā)的協(xié)同演進(jìn)

物理設(shè)計的挑戰(zhàn)推動著EDA軟件的創(chuàng)新,而軟件能力的提升又使得更復(fù)雜的物理設(shè)計成為可能。兩者在以下趨勢中共同發(fā)展:

- 先進(jìn)工藝驅(qū)動:隨著工藝節(jié)點(diǎn)進(jìn)入3納米及以下,物理效應(yīng)(如邊緣放置誤差、量子效應(yīng))愈發(fā)顯著,對物理設(shè)計工具提出了更精細(xì)的建模和優(yōu)化要求。

- 系統(tǒng)級與三維集成:基于芯粒(Chiplet)的異構(gòu)集成和3D-IC技術(shù),使得物理設(shè)計從二維平面擴(kuò)展到三維空間,需要全新的布局、布線和熱分析工具。

- AI/ML的深度融合:機(jī)器學(xué)習(xí)技術(shù)正被廣泛應(yīng)用于預(yù)測布線擁塞、優(yōu)化布局、加速時序簽核等環(huán)節(jié),正在改變傳統(tǒng)物理設(shè)計的方法學(xué)。

- 云化與平臺化:EDA上云(Cloud-EDA)提供了彈性的計算資源,支持大規(guī)模并行任務(wù)。軟件平臺正朝著更開放、更集成、更智能的方向發(fā)展。

###

IC物理設(shè)計是將抽象邏輯變?yōu)槲锢韺嶓w的魔法過程,而EDA軟件開發(fā)則是施展這一魔法的法杖與咒語。沒有先進(jìn)的軟件,面對數(shù)億門級的設(shè)計,工程師將束手無策。物理設(shè)計工程師需要深刻理解軟件工具的能力與局限,而EDA軟件開發(fā)人員則必須洞悉物理設(shè)計的本質(zhì)需求與工藝前沿。二者的緊密協(xié)作與創(chuàng)新,是推動摩爾定律持續(xù)前行、釋放芯片性能潛力的關(guān)鍵力量。