在當今高度信息化的時代,半導體集成電路(IC)作為電子設備的核心,其復雜性與集成度日益提升。為了在研發、生產與應用中有效區分和管理數以萬計的芯片,一套系統而規范的型號命名法應運而生,并與集成電路設計流程緊密關聯,共同構成了半導體產業的技術基石。

一、集成電路型號命名法:解碼芯片的“身份證”

集成電路的型號如同其獨一無二的“身份證”,通常由字母和數字組合而成,遵循一定的命名規則,以傳達關鍵信息。不同廠商雖有各自體系,但大體包含以下核心要素:

- 廠商前綴:標識芯片制造商,如Intel的“IN”、Texas Instruments的“SN”或“TL”、STMicroelectronics的“ST”。

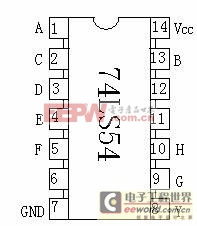

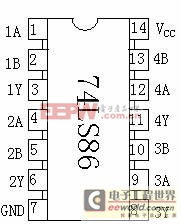

- 系列/功能代碼:指明芯片的類別或主要功能,例如“74”代表通用TTL邏輯系列,“LM”表示線性放大器(如運算放大器),“MAX”常為Maxim公司的模擬信號處理芯片。

- 型號序號:同一系列中區分具體型號的數字,定義了芯片的詳細功能與性能參數,如“7400”是四路2輸入與非門,“LM358”是雙運算放大器。

- 性能/規格后綴:進一步描述工作溫度范圍、封裝形式、速度等級等。例如,“C”代表商業溫度范圍(0°C至70°C),“M”代表軍用溫度范圍(-55°C至125°C),“N”可能代表塑料雙列直插封裝(PDIP)。

示例解析:型號“SN74HC00N”可解讀為:德州儀器(SN)生產的74系列高速CMOS(HC)邏輯芯片中的四路2輸入與非門(00),采用塑料雙列直插封裝(N)。

這套命名法不僅方便了工程師的選型與采購,也反映了芯片的技術代際、工藝特點和市場定位,是連接設計、制造與應用的重要橋梁。

二、集成電路設計:從構思到實現的精密之旅

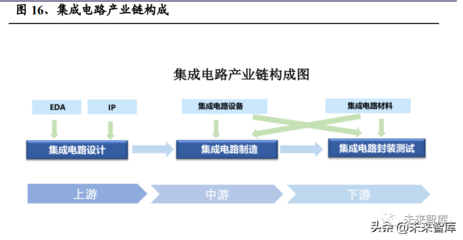

集成電路設計是將系統需求、電路功能轉化為可在硅片上實現的物理版圖的復雜過程。它通常遵循一個分層化、迭代化的設計流程,主要階段包括:

1. 系統架構設計:

定義芯片的整體功能、性能指標(如速度、功耗、面積)和系統級模塊劃分。這需要綜合考慮應用場景、算法需求和工藝制程的約束。

- 前端設計(邏輯設計):

- 功能描述:使用硬件描述語言(HDL),如Verilog或VHDL,編寫寄存器傳輸級(RTL)代碼,精確描述芯片各模塊的邏輯功能與時序行為。

- 功能驗證:通過仿真工具,驗證RTL代碼是否滿足設計規范,確保邏輯正確性。這是發現和修正錯誤的關鍵階段。

- 邏輯綜合:利用綜合工具,將RTL代碼映射到目標工藝庫的標準邏輯單元(如與門、或門、觸發器等),生成門級網表。此過程會進行時序、面積和功耗的初步優化。

- 后端設計(物理設計):

- 布局規劃:確定芯片核心區域、各個功能模塊的擺放位置以及電源/地線網絡的全局規劃。

- 布圖與布線:將綜合后的門級網表中的所有標準單元和宏模塊進行精確擺放(布局),并完成它們之間的所有電氣連接(布線)。

- 時序收斂與物理驗證:進行詳細的靜態時序分析(STA),確保所有信號路徑滿足時序要求;同時進行設計規則檢查(DRC)和版圖與原理圖一致性檢查(LVS),確保版圖符合晶圓廠的制造工藝規則且與網表邏輯一致。

- 版圖交付:最終生成符合要求的GDSII格式版圖文件,交付給晶圓廠進行掩膜制作與流片生產。

三、命名法與設計的交匯:協同與映射

集成電路的型號命名與其設計過程密切相關。設計階段確定的芯片功能、性能等級和采用的工藝技術,最終會凝結在型號名稱中。例如,一個采用先進28納米工藝、面向低功耗移動應用設計的處理器,其型號后綴可能包含“LP”(低功耗)標識;而一個經過汽車級可靠性設計驗證的芯片,其型號中可能體現“Q”或“AEC-Q100”等車規認證信息。

反之,型號命名法也為設計提供了目標和約束。設計師在項目伊始,就需要明確未來芯片的型號定位,這直接指導了架構選型、IP核復用、工藝庫選擇以及最終的測試與封裝方案。

###

半導體集成電路的型號命名法與設計流程,是技術工程化與產品管理智慧的集中體現。命名法是對設計成果的標準化凝練與市場語言翻譯,而設計流程則是實現這一成果的科學方法與技術路徑。二者相輔相成,共同推動著芯片性能的不斷提升與應用領域的持續拓展,支撐著整個數字世界的飛速演進。理解這套體系,對于深入參與半導體產業的研發、生產、銷售乃至應用環節,都具有重要意義。